# High Performance AXI Protocol Based Improved DDR3 Memory Controller With Improved Memory Bandwidth

#### Manoj Gupta a, Dr. Ashok Kumar Nagawat b

<sup>a</sup> Research Scholar, Faculty of Science, University of Rajasthan, Jaipur, India.

#### **Abstract**

The DDR3 Memory has backward compatibility with existing DDR2 Memory and power saving advantage. To increase the performance of DDR3 memory controller, we fire read/write transaction with High speed so require High-speed AXI (Advance extensible Interface) Bus. This paper deals with the high performance AXI protocol based improved DDR3 memory controller with improved memory bandwidth. In this paper, controller clock frequency is 400 MHz and CAS Latency is 10.

**Keywords:** Prefetch Operation, Refresh Operation, AXI Protocol Interface Block, Data Strobe Signal, Write operation, Measurement of bandwidth

#### INTRODUCTION

#### PREFETCH OPERATION:

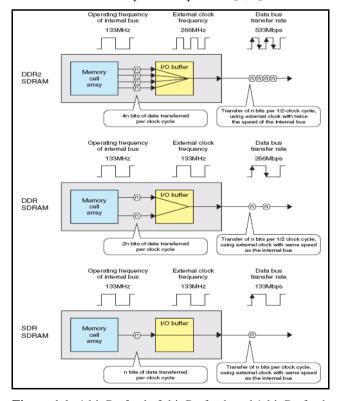

DDR2 SDRAM uses the 4-bit prefetch operation and DDR3 SDRAM uses the 8-bit prefetch operation [1, 4].

**Figure 1.1:** 4-bit Prefetch, 2-bit Prefetch and 1-bit Prefetch Operation in DDR SDRAM

#### Reset:

The Reset pin is used for completely erasing the data in the DDR3 Memory. This is the unique feature available in DDR3 Memory only. This pin should be used with caution because it will remove the complete data [2,3,5].

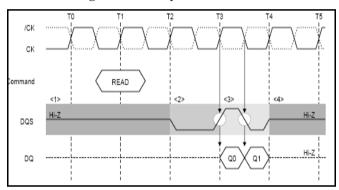

#### Data strobe signal in Read cycle:

Figure 1.2: shown Read data aligned with DOS signal

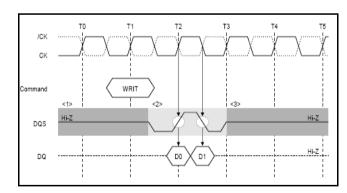

#### Data strobe signal in Write cycle:

Figure 1.3: Shown Write data aligned with DQS signal

#### **DESIGN METHODOLOGY:**

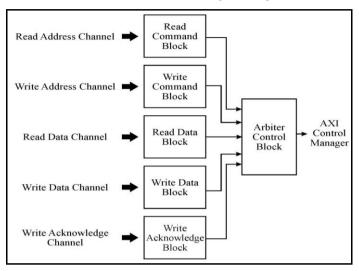

# ARBITER OPERATION (AXI PROTOCOL INTERFACE BLOCK)

Arbiter block has two different inputs write and read commands. Polling priority has been used give service to one of these commands [6, 8]. Write command is served

<sup>&</sup>lt;sup>b</sup> Professor, Department of Physics, University of Rajasthan, Jaipur, India.

first if AW\_LAST of that command is there and command FIFO is not empty. AW\_LAST bit decide that complete data is in FIFO means it count the AW\_LAST bit and when it is not zero then service write command otherwise not. In the read command case when command FIFO is not empty it will issue read command otherwise not [7, 9, 11].

Figure 2.1: Block Diagram of AXI Protocol Interface Block

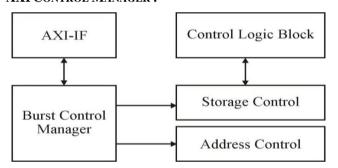

#### **AXI CONTROL MANAGER:**

Figure 2.2 Block Diagram of AXI Control Manager

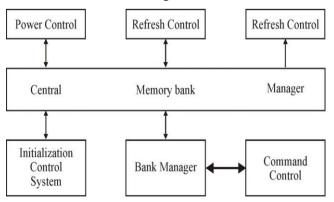

## **DDR3 Memory Controller:** The internal blocks of DDR3 Controller are shown in the figure 2.3.

Figure 2.3 Block Diagram of DDR3 Controller Block

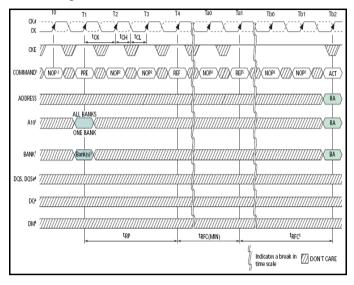

#### **Refresh Command:**

The 1Gb DDR3 SDRAM requires refresh cycles at an average interval of 7.7256µs (MAX). This command is shown in figure 2.4.

Figure 2.4 Refresh Command

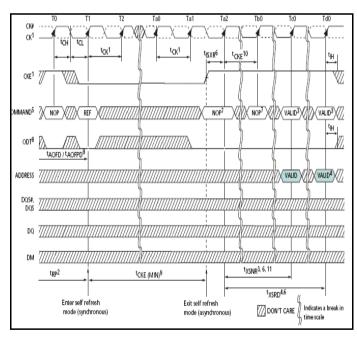

#### **Self Refresh Command:**

Figure 2.5 Self Refresh Command

#### SIMULATION, TESTING AND VERIFICATION

The generator fires the random test pattern of random burst size, burst length and addresses, which gets stored in memory in different locations. Memory is used to store the data and different transactions. Monitor block is being used for sampling and driving the input/output of DUT on the AXI

Protocol. Scoreboard is used to trace the error coming in which location and which transaction [12,15].

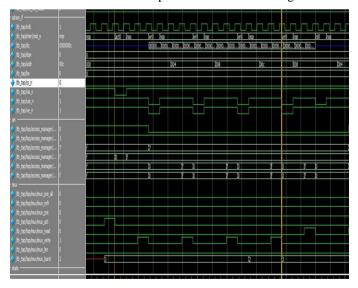

#### **Refresh Operation:**

The DDR3 Memory requires the refresh at an average interval of 7.4 µs. A maximum of eight refresh commands can be posed to any given DRAM [14].

Figure 3.1: Simulation Result of Refresh Operation

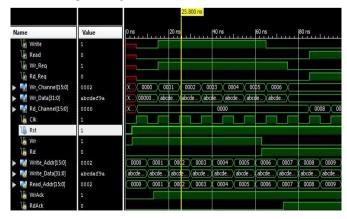

### Write operation serviced by AXI Protocol Interface block:

When aw\_last\_in signal is asserted high and write command FIFO is not empty (aw\_ready asserted high) then we issue write command and if no read command is there we can issue another write command [5]. The all write commands and data are stored in FIFO when aw\_valid and aw\_data\_valid is asserted high respectively and FIFO is not full. The Results for write operation are shown in Figure 3.2.

**Figure 3.2:** Write operation serviced by AXI Protocol Interface block

### Read command serviced by AXI Protocol Interface Block:

When read commad FIFO is not empty (aw\_ready asserted high) then we issue read command and if no write command is there we can issue another read command. The all read commands are stored in FIFO when ar\_valid is asserted high and command FIFO is not full. The read command has higher priority then write command.

Figure 3.3: Read command serviced by AXI Protocol Interface Block

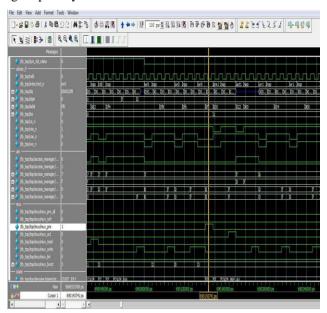

#### Write Response of AXI Protocol Interface Block:

Write response channel has three different signals wready, w\_response and w\_valid\_resp\_out signal. When we pass write command information to Burst manager block then we also store w\_response has OKEY response and when master give wready high then we pass w\_valid\_resp\_out and w\_response information to master [8]. In this simulation result shown (in Figure 3.4) w\_response, wready and w\_valid\_resp\_out signals.

**Figure 3.4:** Write Response of AXI Protocol Interface Block

#### **Measurement Results:**

Measurement Settings:

- Measurement Cycle duration: 200us

- Memory refresh interval is 95% of refresh period in 7.8μs.

- Addition bus turnaround cycle is used.

- Transaction Burst Length is 1,2,4,8,16.

- Optimal address alignment is used.

- Controller Clock frequency is 400 MHz.

- CAS Latency is 10.

Measurement results are represented in percentages of maximum memory bandwidth.

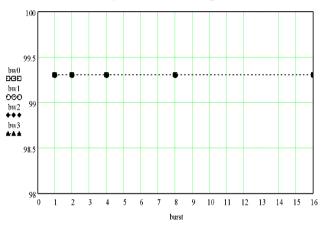

#### • Measurement of bandwidth in sequential write mode

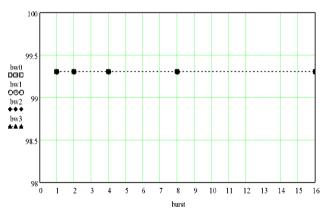

### • Measurement of Bandwidth in sequential read mode

#### **CONCLUSION**

DDR3 SDRAM core architecture doubles the internal data prefetch from 4n-bit wide transfers to 8n-bit-wide transfers. In DDR3-800 SDRAM, the core array only needs to operate at half the data-rate frequency. However, increasing the prefetch to 8n increases the die size because the internal I/O paths are doubled. With half the data rate frequency, but twice the I/O paths, a DDR3-800 SDRAM has the same core frequency as a DDR2-400 device. In addition to core frequency, DDR2 and DDR3 SDRAM will share a similar

migration path. DDR2 SDRAM was defined with 256Mb 4-bank devices at its inception, had 512Mb 4-bank and 1Gb 8-bank devices added for mainstream production, and was eventually developed with 2Gb 8-bank devices for high-capacity memory systems.

#### REFERENCES

- [1] DAEWON HA ET AL(1998) 'SELF-ALIGNED LOCAL CHANNEL IMPLANTATION USING REVERSE GATE PATTERN FOR DEEP SUBMICRON DYNAMIC RANDOM ACCESS MEMORY CELL TRANSISTORS', JAPANESE JOURNAL OF APPLIED PHYSICS, 37(1), NUMBER 3B.

- [2] Chang L et al (1998) Simulation of Semiconductor Processes and Devices: Minimizing Bitline Coupling Noise in DRAM with Capacitor-Equiplanar-to-Bitline (CEB) Cell Structure, pp 324-327.

- [3] Hongil Yoon et al (1999), "A 2.5V 333Mb/s/pin 1Gb Double Data Rate SDRAM", *IEEE Int. Solid State Circuits Conf. (ISSCC) Dig. Tech. Papers*, pp.412-414.

- [4] Pilo H. et al (2003), 'A 5.6-ns Random Cycle 144-Mb DRAM With 1.4 Gb/s/pin and DDR3-SRAM Interface' *IEEE JOURNAL OF SOLID-STATE CIRCUITS*, VOL. 38, NO. 11, NOVEMBER 2003.

- [5] Uk-Rae Cho et al (2003), 'A 1.2-V 1.5-Gb/s 72-Mb DDR3 SRAM', *IEEE JOURNAL OF SOLID-STATE CIRCUITS*, VOL. 38, NO. 11, NOVEMBER 2003.

- [6] B. Bhat et al (2010), 'Making DRAM Refresh Predictable', 2010 22nd Euromicro Conference on, pp. 145-154, 6-9July 2010.

- [7] Kim N.S. et al (2003) 'Programmable and Automatically Adjustable On-Die Terminator for DDR3-SRAM interface', *IEEE 2003 CUSTOM INTEGRATED CIRCUITS CONFERENCE*.

- [8] Ho Young Song et al (2003), 'A 1.2Gb/s/pin Double Data Rate SDRAM with On-Die-Termination', *ISSCC 2003 /* SESSION 17 / SRAM AND DRAM / PAPER 17.8.

- [9] Churoo (Chul-Woo) Park et al (2006), 'A 512-Mb DDR3 SDRAM Prototype With CIO Minimization and Self-Calibration Techniques', *IEEE JOURNAL* OF SOLID-STATE CIRCUITS, VOL. 41, NO. 4, APRIL 2006.

- [10] Sung-Bae Park. "Performance monitor unit design for an AXI-based multi-core SoC platform", Proceedings of the 2007 ACM symposium on Applied computing - SAC 07 SAC 07, 2007.

- [11] X. Yang et al (2009) "DDR3 based lookup circuit for high-performance network processing" *IEEE*

- *International SOC Conference, SOCC 2009.*pp 351-354.

- [12] K. Itoh, et al.(1997), "Limitations and challenges of multigigabit DRAM chip design", *IEEE J. Solid-State Circuits*, vol. 32, pp. 624-634, 1997.

- [13] Ahn Gijung (2000), "A 2-Gbaud 0.7-V Swing Voltage-Mode Driver and On-Chip Terminator for High-Speed NRZ Data Transmission", *IEEE, Journal of Solid-State Circuits*, vol. 35, 2000.

- [14] T. Mladenov (2006), "Bandwidth, Area Efficient and Target Device Independent DDR SDRAM Controller", *Proceedings of World Academy of Science, Engineering and Technology*, Vol. 18, De. 2006, pp. 102-106.

- [15] T. Sunaga, et al (1997)., "An eight-bit prefetch circuit for high-bandwidth DRAM',s ", *IEEE J. Solid-State Circuits*, vol. 32, no. 1, pp. 105-110, 1997.