## Fuzzy Based VAR Control using IM Drive with Nine Switch AC/AC Converter

### Doddabasappa N<sup>1</sup>, Anil Kumar D B<sup>2</sup>, Raghu.C.N<sup>3</sup>, Sagar B S<sup>4</sup>

Assistant Professor, School of Electrical and Electronics Engineering, REVA University, Bengaluru, Karnataka-560064, India.

#### **Abstract**

Reactive power compensation plays an vital role in AC power transmission system. Reactive power is mainly needed to maintain the system voltage while the real power is transmitted through transmission lines. If the reactive power is insufficient, the power cannot be delivered to the loads due to voltage dip. This paper recommended an fresh novel reactive power compensation technique using nine switch converter based Induction Motor drive. The required reactive power can be provided by the induction motor with the help of nine switch converter. A fuzzy logic controller based closed loop is developed for reactive power compensation which can be achieved by handling the front end rectifier voltage using phase shifted spwm technique.

**Keywords:** Digital controller, SRF PLL, 9 switch converter, VAR compensation.

#### INTRODUCTION:

The induction motors usually operates in slow power factor which creates a power quality problems. For avoiding those issues, power electronics based converters with high power factor operation is used in 1,2. High switching frequency devices and digital controllers (3,4) helps in improving the power quality. The industrial loads mainly need reactive power compensation in order to upgrade power factor.

Various induction motor drive techniques are used to upgrade the power factors. The first one is diode bridge rectifier with inverter combination. But this removes the options of developmental braking and also input line current is distorted. To rectify these problems, current injection techniques was used in 5,6. But this increases the size and cost of the circuit. Then the diodes are replaced by active switches with PWM switching techniques(7,8). In this, the distortion in input line current is reduced and also regenerative braking can be achieved but the number of switches was increased and dc link capacitors are to be included. To avoid dc link capacitors, Matrix converters was used(9-11).

In this, reactive power can be compensated with the help of 9 switch induction motor drive. As differentiate to conventional 12-switch converter, the proposed converter has less number of switches count by one-third [12]. Hence the reliability is increased by proposed converter. Easy PWM techniques as SPWM, third harmonic injected SPWM and SVM have been tried[13], [14]. In [15], they are explained and justifying that the usage of NSC for AC-AC operation in constant switching frequency. Where NSC can be illustrated and it can be used effectively in the low loss area boundaries. In variable

frequency mode, the switching of NSC using modified technique of sinusoidal pwm is done[16]. The load is fed with sustained power supply with the help of NSC[17]. To mitigate sag as a FACTS device power quality enhancement NSC is controlled DFIG for WECS is analyzed in [19]. Advanced improvement and comparison of NSC for UPQC is used[20].

Here, the VAR compensation by IM drive with nine switch converter is introduced. A fuzzy based control technique is reorganized for needed var compensation. An reactive power compensation might be reached for variable loads and the system might be executed at togetherness, leading and lagging power factors.

# OPERATION OF NSC AND GENERATION OF GATE SIGNAL

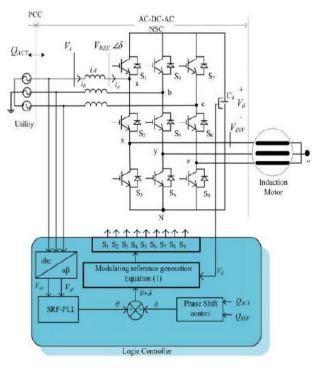

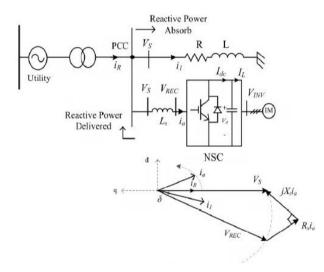

As described in the block diagram given below, the NSC by IM is connected to the feeder with filter inductance *Ls*. The input is given to rectifier nodes and output will be provided by inverter nodes.

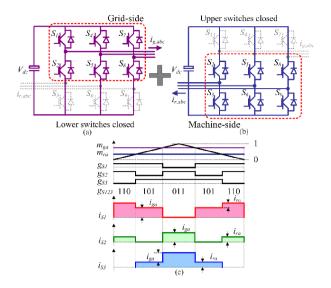

Three legs were situated and each one have three switches in an rectifier mode. Switches S1, S4, and S7 are active (ON-OFF) while; S3s, S6, and S9 switches are ON constantly. In inverter mode S3, S6, and S9 are active (ON-OFF) while; S1, S4, and S7 are ON incessantly. In both rectifier and inverter operation three middle switches are active.

International Journal of Applied Engineering Research ISSN 0973-4562 Volume 13, Number 20 (2018) pp. 14706-14711 © Research India Publications. http://www.ripublication.com

In this, a high-frequency carrier signal and two modulation reference signals are used .Inverter reference must always be lesser than rectifier reference as the rectifier and inverter operates simultaneously. An dc offset is added within rectifier and inverter sinusoidal references as positive and negative respectively to fulfill the switching conditions. The modulating reference for rectifier should be synchronized with grid voltage. The phase angle is extracted from grid voltage using SRFPLL to generate modulation signals for proposed converter as stated by Equation (1).

$$\begin{aligned} V_{\text{r\_a}} &= m_{\text{rec}} sin(\theta + \delta) + V_{\text{offset}} \\ V_{\text{r\_b}} &= m_{\text{rec}} sin(\theta - 120^{\circ} + \delta) + V_{\text{offset}} \\ V_{\text{r\_c}} &= m_{\text{rec}} sin(\theta + 120^{\circ} + \delta) + V_{\text{offset}} \end{aligned}$$

$$\begin{aligned} V_{\text{i\_x}} &= m_{\text{inv}} sin(\theta + \delta) - V_{\text{offset}} \\ V_{\text{i\_y}} &= m_{\text{inv}} sin(\theta - 120^{\circ} + \delta) - V_{\text{offset}} \\ V_{\text{i\_z}} &= m_{\text{inv}} sin(\theta + 120^{\circ} + \delta) - V_{\text{offset}} \end{aligned} \tag{1}$$

For the rectifier operation, modulation references Vr\_a, Vr\_b, and Vr\_c is used and for the inverter operation, modulation references Vi\_x, Vi\_y, and Vi\_z is used.

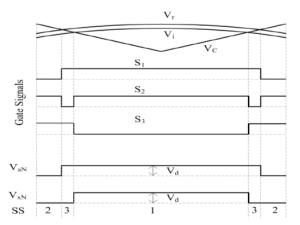

3. Waveforms of gate signal generation.

In the above diagram, when Vr is higher than Vc, a gate pulse for S1 will be high and when Vi is lesser than Vc, a gate pulse for S3 will be high. If we apply NAND logic to gate signals S1 and S3, a gate pulse for S2 is captured. The feasible switching states are given in the above figure. The corresponding leg voltages for rectifier (VaN), switching state (SS) and inverter (VxN) are displayed in Table I.

| SS | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | V <sub>aN</sub> | $V_{xN}$       |

|----|----------------|----------------|----------------|-----------------|----------------|

| 1  | ON             | ON             | OFF            | V <sub>d</sub>  | V <sub>d</sub> |

| 2  | OFF            | ON             | ON             | 0               | 0              |

| 3  | ON             | OFF            | ON             | $V_d$           | 0              |

### **FUZZY LOGIC CONTROL:**

In several control application Fuzzy logic is utilized with high success. Most of the consumer products have fuzzy control such as controlling of room temperature using air-conditioner, anti-braking system, traffic light control, washing machines, etc are few examples of fuzzy controller.

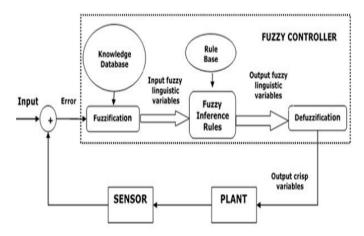

The upcoming diagram displays the architecture of fuzzy logic control (FLC)

Followings are the main factors of the FLC

- **Fuzzifier** In this, the input parameters are converted into fuzzy parameters.

- Fuzzy Knowledge Base It provides the relation between input parameters and output parameters and as per the fuzzy rules set, it will process the input to output fuzzy parameters.

- Fuzzy Rule Base It is the collection of rules set by the user.

- Inference Engine It will process the input to output fuzzy parameters accordingly to the fuzzy rules set. .

- **Defuzzifier** The output fuzzy parameters are converted into actual output parameters..

# OPERATING PRINCIPLE OF THE PROPOSED VAR COMPENSATOR

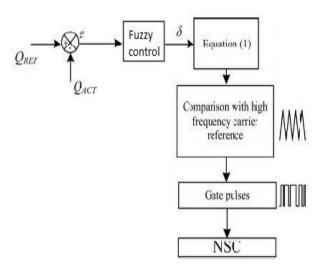

The grid voltage (Vs) and the rectifier input voltage (VREC) decides the amount of required VAR generation by NSC. The dc link voltage Vd depends on the magnitude of VREC. The magnitude of VREC might be managed by varying Vd. The DC link capacitor is charged by managing real power from pcc to capacitor. The real power is controlled by phase shifting of reference at rectifier side wrt the grid voltage with an angle  $\varphi$ . Vd is controlled by controlling angle  $\varphi$ . Therefore, VREC is assorted by managing  $\varphi$  as to get required VAR transfer from grid to NSC. The below diagram design displays the A fuzzy logic control for reactive power compensation.

The QREF is differentiated with measured reactive power (QACT) at grid. The error (e) generated is fed to fuzzy controller. The fuzzy controller provide  $\varphi$  and gives reference reactive power by preserving VREC. For giving phase shift to converter pulses, VREC is used.

In Equation (1) modulation references are given. To gain a gate pulses these are the references are contrast with high frequency carriers. Hence; IM can be operated at leading, unity or lagging power factor with required VAR by maintaining the *VREC* with grid phase voltage. The IM is fixed along with an inductive load at PCC.

An rules set for fuzzy controller in order to provide the angle is given below

| de e | NB | NS | EZ | PS | PB |

|------|----|----|----|----|----|

| NB   | NB | NB | NS | NS | EZ |

| NS   | NB | NS | NS | EZ | PS |

| EZ   | NB | NS | EZ | PS | PS |

| PS   | NS | EZ | PS | PS | PB |

| PB   | EZ | PS | PS | PB | PB |

In the below picture phasor presentation is given.

The current i1 lags from the PCC voltage due to inductive load and reactive power is shifted from grid to load. To remunarate reactive power, the IM is functioned with leading power factor (*ia*leads *Vs*) such that the grid current is in phase with *Vs*. But if the dc voltage increases, the inverter voltage will also increase. To keep it stable, *minv*is should be controlled.

# THE SURVEY OF THE REACTIVE POWER COMPENSATOR

The reactive power flow is related with *Vs* and *VREC* as in the following equation;

$$Q = (V_s^2 - V_s V_{REC} \cos \delta) / X_s$$

where; *Vs* and *Xs* are un changed factors. For SPWM technique, relation of *Vd* and *VREC* is stated by;

$$|V_{REC}| = K_1 V_d$$

Thus,

$$K_1 = m_{\rm rec}/2\sqrt{2}$$

Vd is superinted by an angle  $\varphi$ . From power balance equation an relation between of Vs, VREC, Vd and angle  $\varphi$  is obtained. In this paper ia and Idc are the converter current and dc current respectively. At balanced state, Vd achieved a stable value with Idc even to IL. Idc fulfils the power balance equation and ir is a function of VREC. For getting the bond between dc voltage and phase angle  $\varphi$ , it can be resolved in the d-q frame. Equating converter dc output power and the input power in d-q reference frame:

$$V_d I_{dc} = V_{RECd} i_{ad} + V_{RECg} i_{ag}$$

(5)

The phasor presentation of NSC system is as follows-

$$v_{sd} = V_{RECd} + R_s i_{ad} - X_s i_{ag} \qquad (6)$$

$$v_{sq} = V_{RECq} + R_s i_{aq} + X_s i_{aq} \qquad (7)$$

here

$$V_{RECd} = -\sqrt{3}|V_{REC}|sin\delta$$

(8)

$$V_{RECq} = -\sqrt{3}|V_{REC}|cos\delta$$

(9)

$$v_{sd} = 0$$

(10)

$$v_{sq} = -\sqrt{3}V_s \qquad (11)$$

Rs is practically consistently available in the inductor. Therefore; by taking into consideration of the internal resistance of inductor analysis is done. We can get from the above shown Equation (6) and (7)

$$i_{ad} = -R_s V_{RECd} + X_s V_{sq} - X_s V_{RECq} / (R_s^2 + X_s^2) \ \ (12)$$

$$i_{aq} = -R_s V_{RECq} + R_s V_{sq} + X_s V_{RECd} / (R_s^2 + X_s^2)$$

(13)

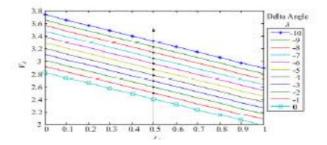

The bond between Vd and power angle  $\varphi$  is shown From Equations (3)-(13

$$V_d = \frac{V_s}{K_1} [\cos \delta - (\frac{X_s}{R_s}) \sin \delta] - I_{dc} \frac{(R_s^2 + X_s^2)}{(3K_1^2 R_s)}$$

(14)

From Equation (4), if mrecD 1 then K1 D 0.3535. The following graphs show the difference in dc voltage to the loading of an converter for different values of  $\varphi$ .

#### RESULT

The laboratory setup for the proposed system is shown in the following diagram:

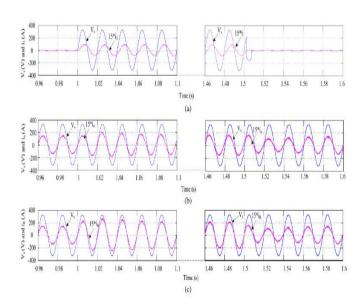

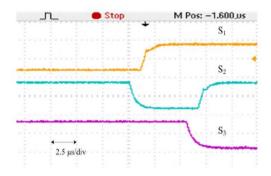

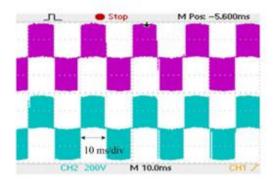

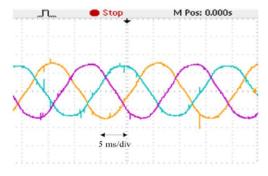

The modulation index at rectifier side is maintained at 0.8 as the modulation index at inverter side is varied in order to maintain inverter output voltage as constant and the switching frequency is provided with 9 kHz. Fig. 12 shows gate pulses for single leg of NSC. Fig. 13 shows rectifier voltage and inverter voltage. Fig. 14 shows three phase current of the Induction motor. The grid is operated at leading, unity and lagging power factor by setting the desired *QREF* and hence the reactive power flow between the grid and the load is controlled.

Diagram10. IM driven by NSC phase voltage and phase current, utility phase voltage and phase current, waveforms of RL load phase voltage-phase current.

Diagram12. Gate pulses of one leg of NSC (20V/div) with 1\_s dead band.

Diagram13. Line voltage of rectifier input and inverter output (200V/div).

Diagram 14. An induction motor current (2A/div)

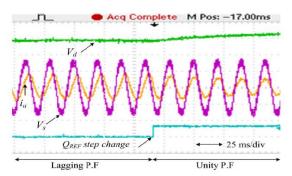

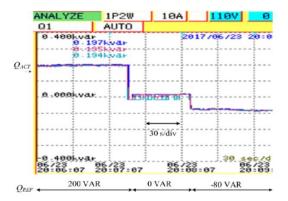

Fig. 15 shows the effect of a step change in *QREF* on power factor and dc link. When it changed from 200 VAR to 0 VAR, it is observed that input current changed from lagging power factor to unity power factor.

Diagram15. Outcome of a step remake in QREF, Vs (100V/div), ia (5A/div) and Vd (50V/div).

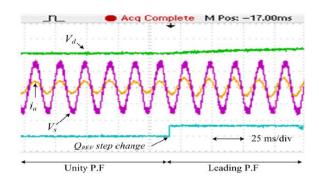

Diagram.16 shows, *Vs*, *ia*, and *Vd* with a step change in *OREF*.

Diagram17. Real per phase reactive power (100VAR/div)

### CONCLUSION

In this paper, an IM drive with NSC for reactive power compensation is proposed. The required reactive power was provided by the induction motor with the help of nine switch converter. A fuzzy logic controller based closed loop is developed for reactive power compensation which can be achieved by handling the front end rectifier voltage using phase shifted spwm technique. The grid is operated at leading and also with unity power factor with the help of Induction motor drive. Mathematical equations are derived to study the relation between dc link voltage and load current with respect to  $\phi$ . Experimental results are proved that the proposed reactive power compensation system is reliable and can be adapted practically.

### REFERENCES

- [1] Y. Song and B.Wang, "Survey on reliability of power electronic systems," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 591\_604, Jan. 2013.

- [2] B. K. Bose, "Energy, environment, and advances in power electronics," *IEEE Trans. Power Electron.*, vol. 15, no. 4, pp. 688\_701, Jul. 2000.

- [3] M. Renge, H. Suryawanshi, and M. Chaudhari, "Digitally implemented novel technique to approach natural sampling SPWM," *Eur. Power Electron. J.*, vol. 20, no. 1, pp. 13\_20, 2010.

- [4] L. Xu, V. G. Agelidis, and E. Acha, "Development considerations of DSP-controlled PWM VSC-based STATCOM," *IEE Proc.-Electr. Power Appl.*, vol. 148, no. 5, pp. 449\_455, Sep. 2001.

- [5] A. M. Cross and A. J. Forsyth, "A high-power-factor, three-phase isolated AC-DC converter using high-frequency current injection," *IEEE Trans.Power Electron.*, vol. 18, no. 4, pp. 1012\_1019, Jul. 2003.

- [6] M. A. Chaudhari, H. M. Suryawanshi, and M. M. Renge, "A three-phase unity power factor front-end recti\_er for AC motor drive," *IET Power Electron.*, vol. 5, no. 1, pp. 1\_10, Jan. 2012.

- [7] R. Lai *et al.*, "A systematic topology evaluation methodology for high density three-phase PWM AC-AC converters," *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 2665\_2680, Nov. 2008.

- [8] Y. W. Li, M. Pande, N. R. Zargari, and B. Wu, "An input power factor control strategy for high-power current-source induction motor drive with active front-end," *IEEE Trans. Power Electron.*, vol. 25, no. 2, pp. 352–359, Feb. 2010.

- [9] M. B. Shadmand, M. Mosa, R. S. Balog, and H. Abu-Rub, "Model predictive control of a capacitorless matrix converter-based STATCOM," *IEEE J.Emerg. Sel. Topics Power Electron.*, vol. 5, no. 2, pp. 796\_808, Jun. 2017.

- [10] O. Ellabban, H. Abu-Rub, and B. Ge, ``A quasi-Z-source direct matrix converter feeding a vector controlled induction motor drive," *IEEE J.Emerg. Sel. Topics Power Electron.*, vol. 3, no. 2, pp. 339\_348, Jun. 2015.

- [11] Y. Sun, X. Li, M. Su, H. Wang, H. Dan, and W. Xiong, "Indirect matrix converter-based topology and modulation schemes for enhancing input reactive power capability," *IEEE Trans. Power Electron.*, vol. 30, no. 9, pp. 4669\_4681, Sep. 2015.

- [12] C. Liu, B. Wu, N. R. Zargari, D. Xu, and J. Wang, "A novel three phase three-leg AC/AC converter using nine IGBTs," *IEEE Trans. Power Electron.*, vol. 24, no. 5, pp. 1151\_1160, May 2009.

- [13] S. M. D. Dehnavi, M. Mohamadian, A. Yazdian, and F. Ashrafzadeh, "Space vectors modulation for nineswitch converters," *IEEE Trans.Power Electron.*, vol. 25, no. 6, pp. 1488\_1496, Jun. 2010.

- [14] F. Gao, H. Tian, and N. Li, "Dead-time elimination method of nine-switch converter," *IET Power Electron.*, vol. 7, no. 7, pp. 1759\_1769, Jul. 2014.

- [15] Z. Qin, P. C. Loh, and F. Blaabjerg, "Application criteria for nine-switch power conversion systems with improved thermal performance," *IEEE Trans. Power Electron.*, vol. 30, no. 8, pp. 4608\_4620, Aug. 2015.

- [16] F. Gao, Z. Li, D. Li, P. C. Loh, Y. Tang, and H. Gao, "Optimal pulsewidth modulation of nine-switch converter," *IEEE Trans. Power Electron.*, vol. 25, no. 9, pp. 2331\_2343, Sep. 2010.

- [17] C. Liu, B.Wu, N. Zargari, and D. Xu, "A novel nine-switch pwm rectifier-inverter topology for three-phase

- UPS applications," in *Proc. Eur. Conf. Power Electron. Appl.*, Sep. 2007, pp. 1 10.

- [18] L. Zhang, P. C. Loh, and F. Gao, ``An integrated nineswitch power conditioner for power quality enhancement and voltage sag mitigation," *IEEE Trans. Power Electron.*, vol. 27, no. 3, pp. 1177\_1190, Mar. 2012

- [19] A. Kirakosyan, M. S. El Moursi, P. Kanjiya, and V. Khadkikar, "A nine switch converter-based fault ride through topology for wind turbine applications," *IEEE Trans. Power Del.*, vol. 31, no. 4, pp. 1757\_1766, Aug. 2016.

- [20] A. M. Rauf, A. V. Sant, V. Khadkikar, and H. H. Zeineldin, ``A novel ten switch topology for uni\_ed power quality conditioner," *IEEE Trans. Power Electron.*, vol. 31, no. 10, pp. 6937\_6946, Oct. 2016.