# **Enhanced Built-In Self Test For MSP 430**

### J.R.Nishanth1 C.Jeevanatham2 S.Sharmila3

PG Scholars 1 3, Department of Electronics and Communication Engineering,

SNS College of Engineering, Coimbatore

Assistant Professor 2, Department of Electronics and Communication Engineering,

SNS College of Engineering, Coimbatore

johnnishanth.j.r@gmail.com, jeeva06@gmail.com,

sharmilashivaswamy@gmail.com.

### **Abstract**

The enhanced Built in self test (BIST) is a combined form of both hardware and software together to resolve the memory problem in self testing. So it automatically comprises own test using self test pattern generation. The implementation can be done using the microcontroller MSP 430 series. Here we are using the Xilinx software for compilation in the design implementation. Also its functional can be done using dynamic RAM and reduces the external testing methods also includes diagnosis of test.

Keywords- BIST, ATE, DRAM

### Introduction

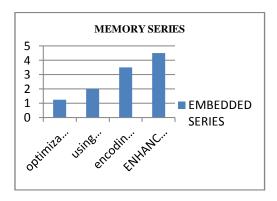

BIST is a perfect solution for automatic generation of an address and data, performing a write to memory, and afterwards performing read and comparing to the expected content of memory cells. It also used in critical circuits directly we cannot involve memory based functions. Better fault coverage can be done. The evolution of BIST is shown in figure 1.

**Figure 1:** evolution of built-in self test

So the special test structures will be produced in the chips. In shorter test times BIST structure can be designed. Capability to produce some testing environment tests in the electrical testing zone. The last merit ensures actually allow the user to produce some more change in functional structure towards the short design implementation. It utilities algorithm such as March c, March c+.the enhanced BIST will be implemented in a internal microcontroller as specified Msp 430 series.

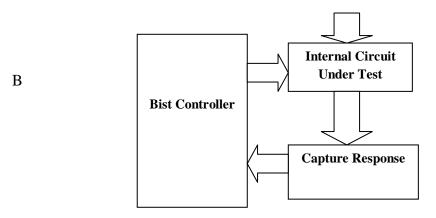

Figure 2: Basic Diagram Of BIST

# **Proposed System**

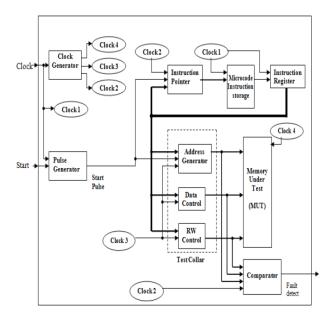

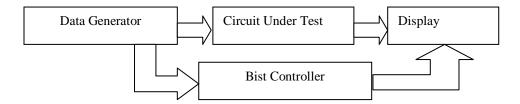

The proposed work contains of enhanced built in self test architecture which automatically generates test pattern and increases speed thereby reduces cost. Here the input test pattern will be generated by its own as in enable value based on the clock pulse functional. The signature gathers the circuit under test to the test pattern as signature. The tests a controller coordinates the actions of the test circuitry and provides a simple external interface.here the test output will be produced towards the pattern generator and introduce a circuit under test hence produce output. Here the enhanced built in self test mentions the automated test pattern generation using the

LFSR (linear feedback shift register) produces a automated test generation in 64 bit memory processing in an instant. Now it can be designed to merge the LFSR coding in Xilinx workbench to produce a schematic to generate a automated test pattern generated. Now mingle the concept of microcode built in self test in main course Msp series.

Figure 3: proposed block diagram of Enhanced BIST

# Methodology

In this enhanced BIST the 64 bits LFSR pattern will be produced and then the value can be denoted. In LFSR pattern generator the test pattern will be produced and the variation of the systematic test pattern generator will be designed. Now the memory value and criteria value can be done towards the system.

Now the microcode BIST architecture will be designed in the functional variations are noted.

# **Memory Bist**

Memory BIST is a functional classification which allows the March blc algorithm that enables in towards a checking and correction of a algorithm. This MBIST acquires a predefined values to assign the functional system to produce a value regarding. This allocates a special memory test procedure to enable a speed memory processing. Conventional block diagram is shown in figure 4.

Figure 4: conventional block diagram for memory BIST

# **March BLC Algorithm**

This algorithm supports a multiple values to be checked with in a given source of time thereby produce a functional binary logic code that generated as enable, clock values, input and output values. This enables a cyclic redundancy coded values the supports a binary error code checking. Clears the faults address and create a redundancy to cyclic checking.

# **Real Time Significants**

- 1. Produces Lower cost of test and avoids external testing equipments

- 2. Better fault coverage so enables a new structure in the memory unit of microcontroller.

- 3. Consumes low power so external testing will also be produced internally.

- 4. Consumers can easily access this system.

- 5. It can support both internal and external enable structure for testing.

# **LFSR Pattern Generator**

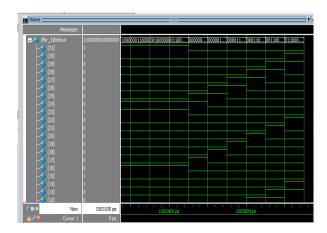

The enhanced BIST produce a variable that can enable a connection design. The output contains a connection in the enable unit that can produce a change in clock values and enable bit values. By changing the binary values towards the system this can be producing the systematic pattern generated in a output. This function LFSR output waveform is shown in below output unit.

**Figure 5:** LFSR pattern generation output

| S.No | Methodology               | Critical Issues             | Solution           |

|------|---------------------------|-----------------------------|--------------------|

| 1.   | Optimization of Microcode | Poor performance by         | Using march BLC    |

|      | Built-In Self Test By     |                             |                    |

|      | Enhanced faults Coverage  | redesign is required to     | microcode BIST     |

|      | for Embedded Memory       | change the test controller. | architecture.      |

| 2.   | New OBIST Using On-       | A new on-chip               | On chip Schmitt    |

|      | Chip Compensation         | oscillation test strategy   | trigger is used as |

|      | of Process Variations     | produces the time           | the on-chip        |

|      | Toward Increasing         | consumption, power          | frequency          |

|      | Fault Delectability in    | consumption.                |                    |

|      | Analog ICs                |                             |                    |

# **Comparison Table:**

### **Simulation Parameters**

The parameters to be considered are enable, reset, input, clock, reset, linear feedback. These parameters are functionally produced in the process towards the built in self test memory so it can be fascinated in the memory.

The modified enhanced built in self test can be probably in the functional systematic memory allocation procedure.

This will consider the power consumption, speed of the processor. Here this consider the functionality endures the memory blocks in the command lines towards the various line of memory values.

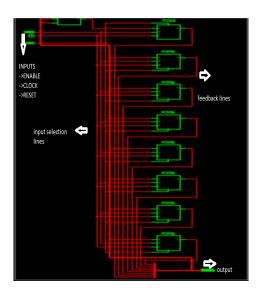

Now its is considered to have the systematic linear feedback towards the input selection lines in the main value, then the output can be done through the various analogy of the memory line as shown in figure 6

Figure 6: Simulation Output

The same output value can change the various values in the considerable memory location. This enables the changing values in the clock value and then can be producing a variation in the functional procedure BIST consider the input value and produce a variation in the LFSR pattern value.

The input value will be changed based on the microcode BIST architecture. Producing new architecture for changing test pattern

The generated value adds sum of the functional variation towards the value in consideration on the value in bits produced so that can reduces the main value system.

This can be promptly the variation in binary coordination in the binary value LFSR random model architecture through the main units.

Figure 7.schematic diagram for BIST

### **Anaysis For Memory Bist**

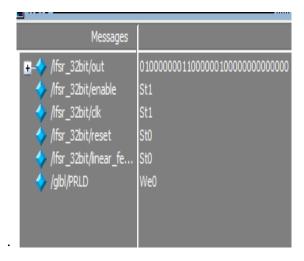

In the analysis stage the short signal will be send towards the memory which will increase the maximum speed of the BIST controller. This simulation is done in the XILINX platform. This will produce the change in the memory perception in the device. The input produces a change in the bit value and enhances the professional systems value by 0 and 1 value in 32 bits random manner, this can be probable produced in memory enhancement in the device as shown in figure 8.

Here we are producing the pattern generator for the LFSR and producing new microcode BIST architecture in order to produce a main functional BIST controller. Combining the two processes together we are designing the enhanced Built in self test for msp 430.

Now the enhanced BIST produces a considerable change in the variation over a main system.

Figure 8: Analysis Parameter For Memory BIST

#### Conclusion

Here the BIST controller provides a wide testing procedure that enables a main functional access to the systemic checking in the memory allocation procedure It is a system performs a dynamic internal and external testing equipments that allows a variable testing in a considerable units. This system avoids the external test improves an incorporation of hardware and software systems. Error rates will be minimum so this advances a connection towards the systematic unit binary code enabling

### Reference

- [1] Mohd Yamani Idna Idris, Mashkuri Yaacob, Zaidi Razak, "A VHDL Implementation Of UART Design with BIST capability"

- [2] Dr. T.V.S.P. Gupta, Y. Kumari, M.Asok Kumar" UART realization with BIST architecture using VHDL" International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 1, January -February 2013, pp.636-640

- [3] M.S. Harvey, Generic UART Manual, Silicon Valley, December 1999

- [4] P. J. Anderson, "The designer's guide to VHDL", Morgan Kaufman, 2nd edition, 2002.

- [5] Neil H.E. Weste, Kim Haase, David Harris, A. Banerjee, "CMOS VLSI Design: A circuits and Systems Perspective", Pearson Education.

- [6] K. Zarrineh, and S. J. Upadhyaya, "On programmable memory built-in self test architectures", Design, Automation and Test in Europe Conference and Exhibition 1999. Proceedings, 1999, pp. 708-713.

- [7] Sandra Irobi Zaid Al-Ars Said Hamdioui.Memory Test Optimization for Parasitic Bit.

[8] N. Z. Haron, S.A.M. Junos, A.S.A. Aziz, "Modelling and Simulation of Microcode Built-In Self test Architecture for Embedded Memories", In Proc. of IEEE International Symposium on Communications and Information Technologies pp. 136-139, 2007.

- [9] S. Hamdioui, Z. Al-Ars, A.J. van de Goor, "Testing Static and Dynamic Faults in Random Access Memories", In Proc. of IEEE VLSI Test Symposium, pp. 395-400, 2002.

- [10] S. Hamdioui, et. al, "Importance of Dynamic Faults for New SRAM Technologies", In IEEE Proc. Of European Test Workshop, pp. 29-34, 2003.

- [11] International SEMATECH, "International Technology Roadmap for Semiconductors (ITRS): Edition 2001".

- [12] A.J. van de Goor, "Testing Semiconductor Memories, Theory Practice" Com Tex Publishing, Gouda, Netherlands, 1998.

- [13] A.J. van de Goor and Z. Al-Ars, "Functional Fault Models: A Formal Notation and Taxonomy", In Proc. of IEEE VLSI Test Symposium, pp. 281-289, 2000.

- [14] "Xilinx ISE 6 Software Manuals and help PDF Collection", http://toolbox.xilinx.com/docsan/xilinx7/ books/manuals.pdf

- [15] Zarrineh, K. and Upadhyaya, S.J., "On Programmable memory built-in self test architectures," Design, Automation and Test in Europ Conference and Exhibition 1999. Proceedings, 1999, pp. 708-713

- [16] Sungju Park et al, "Microcode-Based Memory BIST Implementing Modified March Algorithms", Journal of the Korean Physical Society, Vol. 40, No. 4, April 2002, pp. 749-753 SCEECS 2012

- [17] A.J. van de Goor, "Using March tests to test SRAMs", Design & Test of Computers, IEEE, Volume: 10, Issue: 1, March 1993 Pages: 8-14.

- [18] R. Dekker, F. Beenker and L. Thijssen, "Fault Modeling and Test Algorithm Development for Static Random Access Memories",

- [19] R. Dekker, F. Beenker, L. Thijssen. "A realistic fault model and test algorithm for static random access memories". IEEE Transactions on CAD, Vol. 9(6), pp 567-572, June 1990.

- [20] B. F. Cockburn: "Tutorial on Semiconductor Memory Testing" Journal of Electronic Testing: Theory and Applications, 5, pp 321-336 1994 Kluwer Academic Publishers.