# Design And Implementation Of Resistive Threshold Logic In Dsm Technology

## Dr.S.Govindarajulu<sup>1</sup>

<sup>1</sup>Professor, Department of ECE,

RGMCET, Nandyal, Andhra Pradesh, India.

India. Email: rajulusg09@gmail.com

## C.P.V.N.V.S.Jyosthna Devi<sup>2</sup>

<sup>2</sup>PG scholar, Embedded Systems, Department of ECE, RGMCET, Nandyala, Andhra Pradesh,

India Email: cpvnvsjosh@gmail.com

Abstract- In this project a resistance based threshold logic family which is useful in mimicking brain like large variable logic functions in VLSI is proposed. The concept of resistive threshold logic which minimizes the number of components and design complexity in order to implement large variable Boolean logic functions such as multiplexers, adders is presented. A universal Boolean logic cell based on an analog resistive divider and threshold logic circuit is proposed. Resistive threshold logic comprises of a resistive divider and a threshold logic circuit. The resistive divider is implemented by using active resistors, and provides output voltage as the summation of weighted products of input voltage. The output of this resistive divider is converted as a binary value by a threshold operation, which in turn is implemented by using CMOS inverter. Thus a universal cell structure is presented in order to reduce the overall implementation complexity and in some applications where the number of input variables increases to a very high number this proposed cell is expected to offer an advantage of lesser silicon area, simplicity in designing and enhanced performance when compared to the respective conventional CMOS logic circuits. Experimental results show that this proposed resistive threshold logic features a reliable reduction in circuit area, power dissipation in comparison with CMOS logic design. Synthesis and simulation can be done by using Tanner EDA.

Index Terms-- CMOS logic circuits, active resistors, resistive circuits, threshold logic, multiplexers, adders, DSM technology, Tanner EDA.

#### INTRODUCTION

Boolean algebraic expressions obtained from truth tables are implemented by using the logic gates. In digital integrated circuits like microprocessors and ASICs with the increase in functional requirements resulted in complex logic state implementations. When these complex set of logic states are represented in the form of a truth table they may result in having a large number of input and output variables. As when the number of input variables increases, it may not be possible to manually reduce these boolean logic expressions to reduce the number of components required for its implementation. For this the most common approach used to reduce the number of components required with a large number of variables is by using logic minimization based on prime implicant logics. Techniques, such as Karnaugh map [1], QuineMcCluskey [2], Petrick's method, Buchberger's algorithm [3], and Espresso minimization algorithm [4], are the most commonly used approaches. But, when there is significant increase in number of inputs, these logic minimization techniques may also be not that efficient. In addition to this, the implementations which are made by using these existing logic families become challenging as they are often restricted by the gate delays, the number of inputs, and the number of components. The common approach employed to implement boolean algebra with a large number (>10) of variables, is to apply the minimization techniques for standard gates with a limited number of inputs (<10). But this always leads to increase in number of circuit elements results in more number of circuit elements than that was possible with gates that could support as many number of inputs as the number of variables. In addition to this issue, from one boolean logic to another, to implement a gate the required components number may vary, thus resulting in increased structural complexity and imparting the difficulties in production scale verification ant testing cycles.

Generic digital circuits, like adders can be used to implement *n*-input boolean logic functions. In order to implement 4bit or 8bit or 16 bit adders inputs to the basic logic gates increases, a typical AND-OR logic will have large number of inputs per each gate for its implementation. Hence in implementing large variable boolean logic functions, we

introduce the concept of resistance threshold logic with which design complexity number of components can be reduced. The proposed resistive threshold logic is made up of a resistive divider and a threshold logic circuit.

## PROPOSED CELL

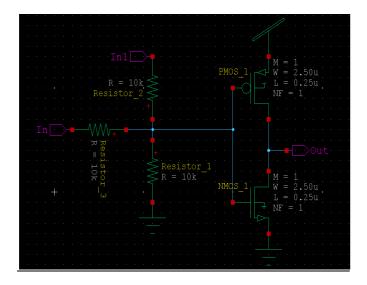

The proposed logic cell, shown in Fig. 1, has a resistive divider and a variable threshold inverter. Digital values which can be equated to the digital logic gate's logic inputs are the inputs to the resistive divider. Depending upon the predefined inverter threshold and the output of the resistive divider, we propose to implement the basic Boolean logic functions.

Fig. 1. Circuit diagram of the proposed resistive divider Boolean logic cell that consists of a two input resistive divider and a variable threshold CMOS inverter

An *N*-input resistance divider circuit consists of one reference resistor  $R_0$  and N input resistors  $R_i$ . The output voltage  $V_0$  for N-input voltage  $V_i$  can be represented as:  $V_0 = \sum_{i=1}^{N} (Vi/Ri)/[(1/R0) + \sum_{i=1}^{N} (1/Ri)]$ . The inputs  $V_i$  may have either the logical level  $V_H$  or  $V_L$  representing a binary logic [1, 0]. We keep equal values to  $R_i$ 's and  $R_0 = mR_i$ , which results in:  $V_0 = (\sum_{i=1}^{N} Vi)/[(1/m) + N]$ .

## LITERATURE SURVEY

One simple approach to implement the resistors used in the resistive divider circuit is by using semiconductor resistors. These semiconductor resistors are made up of a resistive body which is surrounded by an insulator and is developed over a substrate, two contact terminals are implemented by using conductive metallic strips. The semiconductor resistance value is obtained from the expression,  $(\rho L)/(X_j W)$ , where  $\rho$  is the resistivity, L is the length,  $X_j$  is the thickness of the layer, and W is the resistive body width. But when the number of inputs increases while using these semiconductor resistors, the leakage current

becomes very high through the semiconductor resistors. Hence to overcome this drawback the semiconductor resistors are being replaced with active resistors [5].

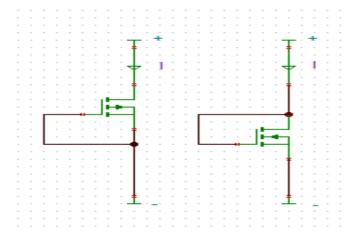

Three terminal transistor the active device, by proper connection it can be converted into a two terminal device resistor called an active resistor. This active resistor can be implemented by simply connecting the gate of an n-channel or p-channel enhancement MOS device to the drain. For the nchannel device the source should be placed at the most negative power supply voltage V<sub>ss</sub> if possible in order to eliminate the bulk effect, the source of the p-channel device should be taken to the most positive voltage for the same reason.. This active resistors can be used in place of polysilicon7 or diffused semiconductor resistors as they offer small signal resistance and also can be used to produce a DC voltage thus when the number of inputs increases the active resistor usage reduces the area consumption and also the collective forward current through the circuit does not increase significantly when compared to using of semiconductor resistors.

Fig.2. (a) n-channel enhancement active resistor (b) p-channel enhancement active resistor

TABLE.I.TRUTH TABLE OF TWO INPUT RESISTIVE DIVIDER LOGIC CELL WHEN USED AS NAND AND NOR GATES

| Input (Vi) | Voltage     | Output<br>Voltage  | NAND             | NOR     |

|------------|-------------|--------------------|------------------|---------|

| $V_1$      | $V_2$       | $V_0$              |                  |         |

| $V_{L}$    | $V_{\rm L}$ | $2V_{L}/3$         | $V_{\mathrm{H}}$ | $V_{H}$ |

| $V_{L}$    | $V_{H}$     | $(V_L+V_H)/3$      | $V_{H}$          | $V_{L}$ |

| $V_{H}$    | $V_{\rm L}$ | $(V_L + V_H)/3$    | $V_{\rm H}$      | $V_{L}$ |

| $V_{H}$    | $V_{H}$     | 2V <sub>H</sub> /3 | $V_L$            | $V_L$   |

Threshold range of NAND:  $(V_L+V_H)/3 < Vth < 2V_H/3$ Threshold range of NOR:  $2V_L/3 < Vth < (V_L+V_{H)3}$  Table.1 shows the truth table of a resistive divider logic cell with two inputs, that implements the NAND and NOR gates by using a predefined inverter threshold Vth. Assuming that  $V_{DD}=1V,\ V_H=1V,\ V_L=0V$ , from the above table it is clear that if the threshold voltage of the inverter is set between 0V and 1/3V, the cell works as NOR logic and if it is between 2/3V and 1/3V the cell works as NAND logic. That means by varying the threshold voltage of the inverter, NAND and NOR logic can be implemented using a single cell.

Generally the range of threshold voltage, Vth of NOR gate is  $(NmV_L/(1+Nm)) \leq V_{th} \leq (((V_H+(N-1)V_L)m)/(Nm+1))$ , and NAND gate is,  $((m\ (V_L+(N-1)V_H))/(Nm+1)) \leq V_{th} \leq (mNV_H/(Nm+1))$ . To find the m value, the lower limit of NAND gate threshold range  $(m(V_L+(N-1)V_H)/(Nm+1))$  is equated to  $(V_H+V_L)/2$ . Now by assuming that  $V_L=0V$  then we get the m value as 1/(N-2) hence we can say that the threshold voltage of NAND gate must be between  $(V_H+V_L)/2$  and  $mNV_H/(Nm+1)$ .

The threshold voltage of the MOSFET dependends on many parameters, like substrate bias voltage Vbs, the surface potential  $\varphi s$ , and substrate doping concentration. The threshold voltage Vtn of the MOSFET can be varied by changing its substrate bias, Vbs. The dependence of substrate bias and the threshold voltage is expressed as, Vtn =  $Vtn_0+K_1(\sqrt{\varphi s} - Vbs - \sqrt{\varphi s})+C$  where  $Vtn_0$  is the zero bias threshold voltage, the surface potential  $\varphi s = 2(k_B T /q)$ ln(Na/n<sub>i</sub>), K1 is a parameter derived by considering nonuniform doping and short channel effects  $K1 = \gamma 2$  -body bias coefficient when substrate doping concentration is equal to  $N_{ch}$  and  $N_{sub}$ , respectively. $\gamma 1 = \sqrt{2q} \in Si \ Nch/Cox$ ,  $\gamma 2 = \sqrt{2q \in Si \, Nsub/Cox}$  and  $V_{bm}$  is the maximum substrate bias voltage. And C shows the effect of narrow channel on threshold voltage. The threshold voltage of the inverter can be represented as,  $Vth = ((Vtn + (V_{DD} - |Vtp|))$  $\sqrt{\mu p Wp/\mu nWn} / (1 + \sqrt{\mu p Wp/\mu nWn})$ , which shows the role of the threshold voltages of the MOSFETs in determining the threshold of the inverter.

## APPLICATION DESIGN

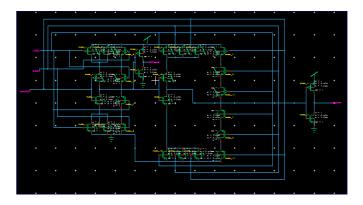

The conventional CMOS design of 16-bit full adder [6][7] is compared with the proposed logic and the simulation is performed in Tanner EDA using a feature size of  $0.25 \mu m^2$ .

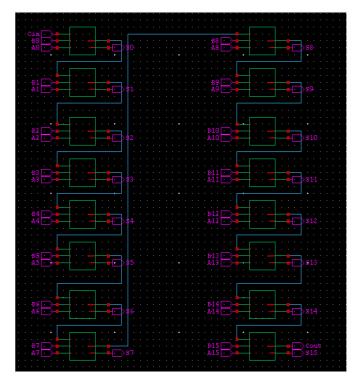

Fig.3. conventional CMOS schematic diagram of Full Adder

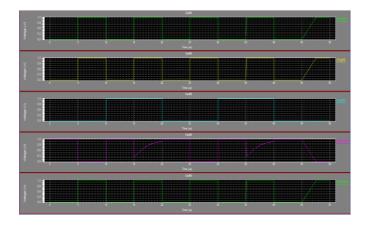

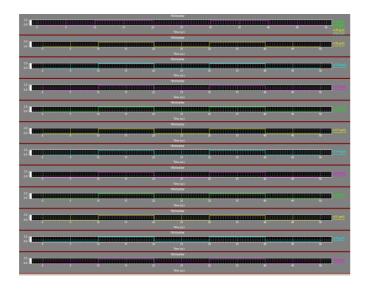

Fig.4. Schematic Wave Form

Fig.5. Conventional CMOS schematic diagram of 16Bit Adder

Fig.6. Schematic Wave Form

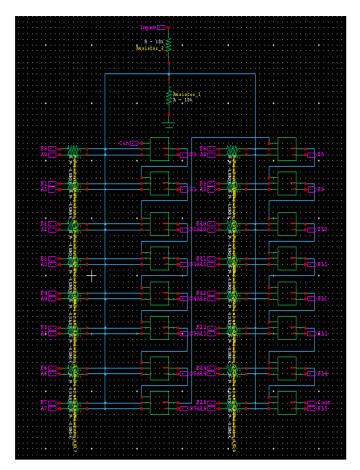

Fig.7. Implementation of 16Bit Adder using proposed logic

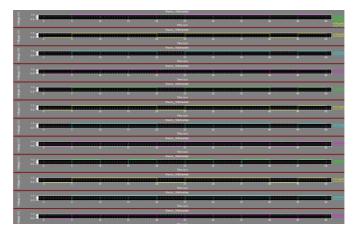

Fig.8. Schematic Wave Form

## **SYNTHESIS REPORT**

TABLE.2.COMPARISON OF 16BIT FULL ADDER CIRCUIT IMPLEMENTED USING RESISTIVE THRESHOLD LOGIC WITH THAT OF CMOS LOGIC

|                                 | Ī                    |                      |

|---------------------------------|----------------------|----------------------|

| Parameter                       | Logic Family         |                      |

|                                 | CMOS logic           | Resistive logic      |

| Temperature                     | 25 (deg C)           | 25 (deg C)           |

| Average<br>Power<br>consumed    | 4.124579e-006w       | 4.650816e-003w       |

| Static Power dissipation        | 6.26122e-002w        | 4.077555e-002w       |

| Dynamic<br>Power<br>dissipation | 5.502783e-007w       | 2.0389376e-009w      |

| Nodes                           | 36                   | 35                   |

| Area                            | 1.680mm <sup>2</sup> | 1.680mm <sup>2</sup> |

Table.2 shows the synthesis report of full adder in both the logics, and this table demonstrates that when 16bit full adder is implemented by using proposed logic even though the average power consumption has increased when compared to the CMOS logic but static power dissipation and dynamic power dissipations are reduced which indicates the reduced power dissipation. Area is almost the same in both the logics.

#### **CONCLUSION**

The resistive threshold logic concept is presented in an application to implement an adder. This logic because of its ability in supporting the large number of inputs, helps in reducing the design complexity. Although this proposed logic outperforms the CMOS logic implementations of large input gates in performance parameters like power (dissipation), area further developments on low power consumption are required. The resistive threshold logic can be extended to the organic circuits, carbon nanotube technologies. And also ue to the ability of the proposed threshold logic in producing the logic gates with large number of inputs, this can be considered as a worth early step of advancement for achieving the kind of goals like mimicking brain like large variable boolean logic applications in VLSI where the design complexity and number of components required are the major areas of consideration.

#### **REFERENCES**

- [1] K. Dean, "An extension of the use of Karnaugh maps in the minimization of logic functions," *Radio Electron. Eng.*, vol. 35, no. 5, pp. 294–296, 1968.

- [2] H. Hwa, "A method for generating prime implicants of a boolean expression," *IEEE Trans. Comput.*, vol. 23, no. 6, pp. 637–641, Jun. 1974.

- [3] L. Bachmair and H. Ganzinger, "Buchberger's algorithm: A constraint based completion procedure," in *Proc. 1st Int. Conf. Constr. Comput. Logics Conf.*, Sep. 1994, pp. 285–301.

- [4] P. McGeer, "Espresso-signature: A new exact minimize for logic functions," *IEEE Trans. Very Large Scale Integr (VLSI)*, vol. 1, no. 4, pp. 432–440, Apr. 1993.

- [5] Prasanth.N, Likhith B P, Naveed Anjum, Gajendra K A "Analysis of active resistors realized using CMOS technology" *IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) Volume 4, Issue 2, Ver. III (Mar-Apr. 2014), PP 07-11 e-ISSN: 2319 4200, p-ISSN No. : 2319 4197.*

- [6] Aravind kumar and Anil kumar Goyal, "Study of various full adders using Tanner EDA tool," in International Journal of Computer Science and technology, IJCST Vol. 3, Issue!, Jan-March 2012.

- [7] G.Vinutna Ujwala, K.Babulu, "VLSI design of one bit full adder using 0.25  $\mu$ M CMOS technology," in *Proc.of AECE-IRAJ Int. Conf.*, 14<sup>th</sup> july 2013, Tirupati, India, ISBN:978-81-927147-9-0.

- [8] C. H. J. Roth, Fundementals of Logic Design, Boston, MA: PWS-Kent, 1995.

#### Author's biodata:

**Dr.Salendra.Govindarajulu**<sup>1</sup> is working as a professor in the Dept. of Electronics and Communication Engg. At RGMCET, Nandyal, Andhra Pradesh, India. He completed B.Tech in ECE in RGMCET, Nandyal, JNYUH, M.Tech in NITC, Calicut and Ph.D in JNTUH, Hyderabad. He presented more than 40 International/National Technical Papers. He is a Life Member of ISTE, New Delhi and Life Member of IAENG. His interest includes Low Power VLSI CMOS Design, Wireless Communications, Electromagnetics, Signal Processing, Analog and Digital IC Design, Mixed Signal design, Analog and Digital Communications, Power Electronics, Image Processing